Tagged VHDL

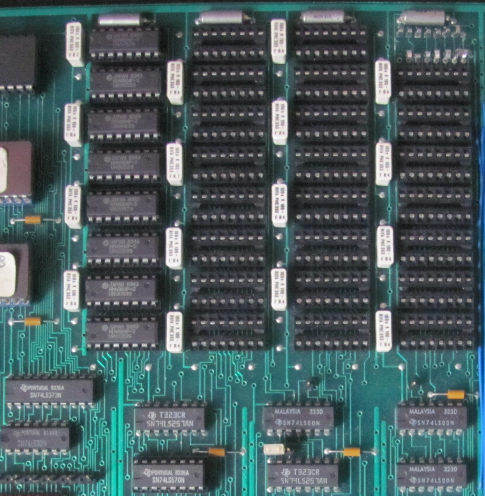

UPNOD 3: The RAM.

Posted on by Idorobots

After a lengthy break I'm back to the UPNOD series. This time we'll take a closer look at the dynamic random-access memory (DRAM) circuitry present on the PCB:

As usual, all of my findings can be found here.

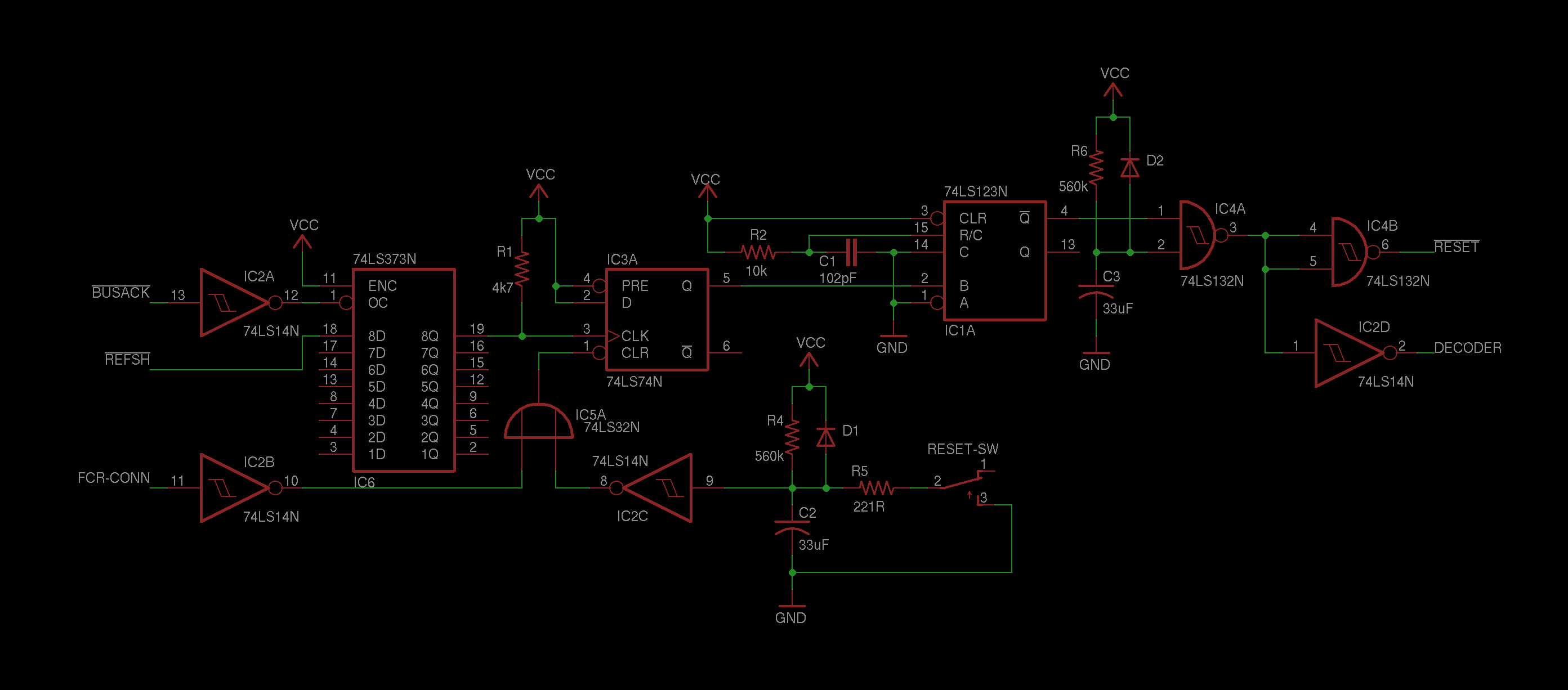

Continue readingUPNOD 2: The reset circuit.

Posted on by Idorobots

A second installment in the UPNOD series, this time we'll take a look into the reset circuitry of the telco card.

As the title implies, this circuit is responsible for generating a proper Z80' reset sequence. Z80, being a rather dumb piece of clever electronics, may boot up in an undesirable undefined state and requires a few cycles of special treatment to properly initialize internal register values. This circuit does just that - it generates the initial reset pulse and handles reset signals coming from other parts of the board, all while maintaining proper synchronization.

Continue reading